# HIGH EFFICIENCY X-KU BAND MMIC POWER AMPLIFIERS

Mike Cardullo\*\*\*, Charles Page\*\*, Douglas Teeter\*, Aryeh Platzker\*

\*Raytheon Company

Advanced Device Center

362 Lowell St

Andover, MA 01810

(508) 470 9402

\*\*Samsung Electronics

Samsung Microwave

Semiconductor

1530 McCarthy Blvd.

Milpitas, CA 95035

\*\*\*Motorola

CSPD

5005 East McDowell Rd.

Phoenix, AZ 85008

## ABSTRACT

MMIC power amplifiers with 3.5 W nominal output power and 49.5% peak power added efficiency over the 8-14 GHz band are described. Efficiency in excess of 40% is obtained over much of the band. The amplifiers utilize Raytheon's power PHEMT technology. Details of the device performance, circuit design, and evaluation are given. The results presented represent state of the art performance for MMIC circuits over X-Ku band.

## INTRODUCTION

Broadband high efficiency power amplifiers are of extreme interest for the development of high efficiency T/R modules. Since the overall efficiency of a module is determined primarily by the power amplifier, every effort must be made to maximize the efficiency of the PA. Several authors have reported respectable PA results over the X-Ku band [1]-[4]. The MMICs described in these papers all operate at the 1 to 2 Watt level.

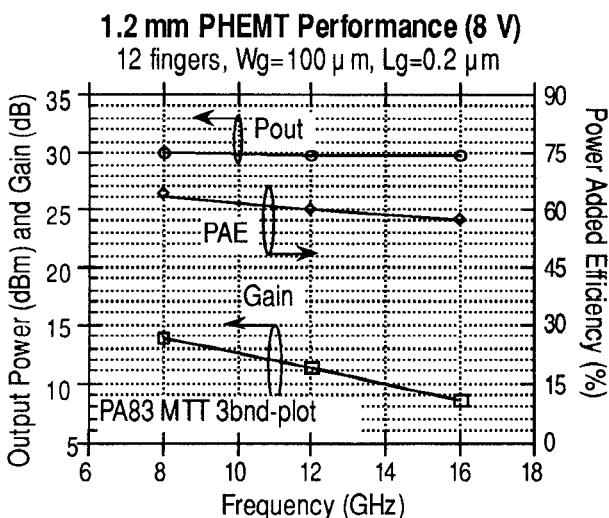

Figure 1. Typical 8V tuned Power data for 1.2 mm PHEMTs.

Earlier work reported by Raytheon described the development of 3 Watt PHEMT based power amplifiers with 40% power added efficiency over the 8-13 GHz band [5]. By using an improved PHEMT device and redesigning the matching networks, we were able to further enhance the amplifier performance. In this paper, we describe AlGaAs/InGaAs/GaAs PHEMT based 2 stage power amplifiers with 3.5 W nominal output power over the 8-14 GHz band. Peak efficiency of 49.5% was obtained and efficiency >40% was measured over much of the band.

## DEVICE CHARACTERISTICS

The amplifiers were designed using Raytheon's power PHEMT process. Devices used standard e-beam defined 0.2  $\mu$ m tri-layer T-gates. Conventional mesa technology was used to define the active areas followed by deposition of NiAuGe to form alloyed ohmic contacts. Gate recessing was performed using both wet and dry etching techniques with TiPtAu being used as the gate metal. Processing is completed by thinning the wafers to 4 mil, etching via holes, and depositing backside metallization. A detailed discussion of the device development can be found in reference [6].

Typical 8 V tuned power data for 1.2 mm PHEMTs is shown in figure 1. These PHEMTs typically provide 29.5-30 dBm output power with 10 dB associated gain and 58% PAE at 14 GHz under 8 V drain bias.  $I_{max}$  values are 580-620 mA/mm and gate-drain breakdown is 10-12 V. Devices used for this work had approximately 1.5 dB more gain than the devices used in reference [5]. The improved gain is attributed to the use of a higher Indium content in the channel of the PHEMT.

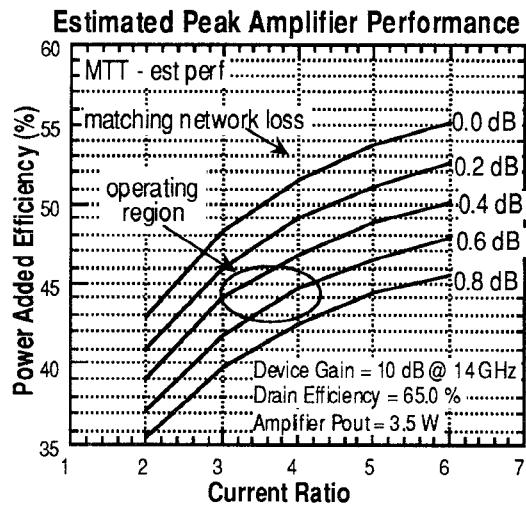

Figure 2 shows the estimated peak efficiency performance for a 2 stage power amplifier based on the tuned device data shown in figure 1. Matching network loss is assumed to be the same for the input, interstage, and output matching networks. While this is clearly not the best assumption, the PAE perfor-

TU

3A

mance of a 2 stage amplifier is limited primarily by the output loss and ratio of 2nd stage to 1st stage drain current. Provided that the first stage is sufficiently sized to drive the output stage into compression, figure 2 should provide a ball park estimate for 2 stage PA performance. Based on this device data, expected 2 stage amplifier efficiency was in the mid forties for 8 V drain bias.

Figure 2. Estimated peak efficiency performance for a 2 stage power amplifier based on the tuned device data shown in Figure 1.

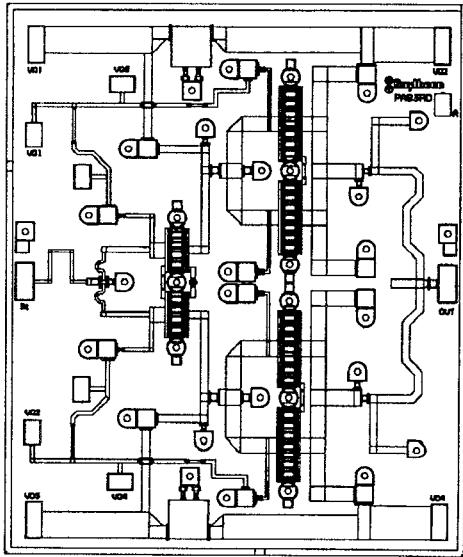

Figure 3. 2 stage PA with 2x(10x100  $\mu\text{m}$ ) PHEMTs driving 4x(16x100  $\mu\text{m}$ ) PHEMTs. Chip dimensions are 3.64 mm x 4.34 mm.

## CIRCUIT DESIGN

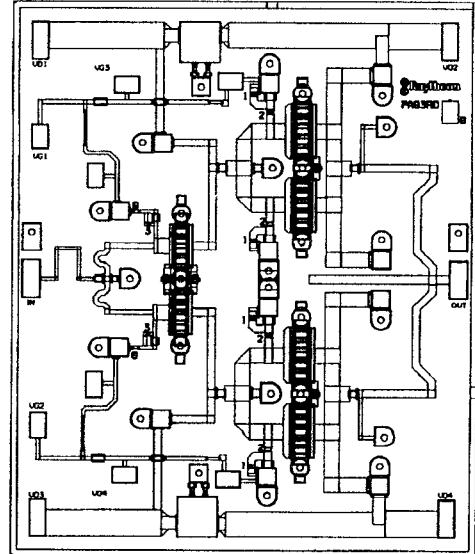

Two different designs were developed and analyzed. Circuit A, shown in figure 3, uses 2x(10x100  $\mu\text{m}$ ) driving 4x(16x100  $\mu\text{m}$ ) PHEMT devices. Input and output matching is to 50 ohms. The output matching network utilizes a shunt C, series C, shunt L configuration for enhanced bandwidth. Circuit B, shown in figure 4, uses 2x(10x100  $\mu\text{m}$ ) driving 4x(12x135  $\mu\text{m}$ ) PHEMT devices. The output matching network utilizes only a series C, shunt L configuration. Circuit B has the same layout as the PA55 amplifier reported in reference [5]. Circuit A uses a higher order matching network in an attempt to improve the bandwidth and high end performance of the amplifier beyond the results reported in reference [5].

Load pull measurements were used to establish the proper load targets for power and efficiency. For both circuits, the output stage was efficiency matched ( $R_{\text{opt}} = 57.1 \text{ ohm-mm}$ ,  $C_{\text{opt}} = -0.425 \text{ pF/mm}$ ) and the driver stage was power matched ( $R_{\text{opt}} = 27.9 \text{ ohm-mm}$ ,  $C_{\text{opt}} = -0.33 \text{ pF/mm}$ ). The input network was optimized for gain flatness using a combination of reactive and lossy mismatch techniques. A complete stability analysis was performed using the method developed in references [7] and [8]. Moding resistors (24 ohms) were added between adjacent gate and drain manifolds in order to prevent small imbalances from generating oscillations. In addition, small resistors were used on the short circuited tuning stubs feeding the gate lines (8 ohms for the first stage and

Figure 4. 2 stage PA with 2x(10x100  $\mu\text{m}$ ) PHEMTs driving 4x(12x135  $\mu\text{m}$ ) PHEMTs. Chip dimensions are 3.64 mm x 4.34 mm.

2 ohms for the second stage). All these resistors were included in the RF simulations so that any minor effects on the matching networks could be accurately accounted for. Finally, bias resistors (100 ohm-mm) were included on the gate bias lines for both stages. A detailed discussion of the design tradeoffs for stability can be found in reference [5].

1.2 mm (12x100  $\mu\text{m}$ ) devices were fully characterized and modeled. Multi bias S parameter mea-

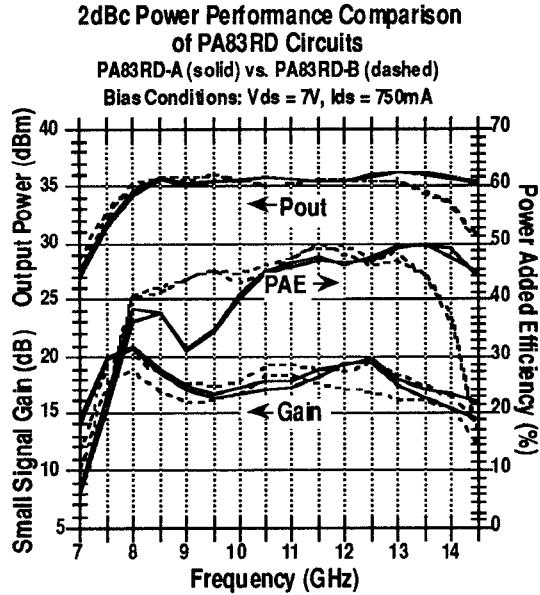

Figure 5. Measured power performance of circuits A and B at 7 V, 750 mA bias.

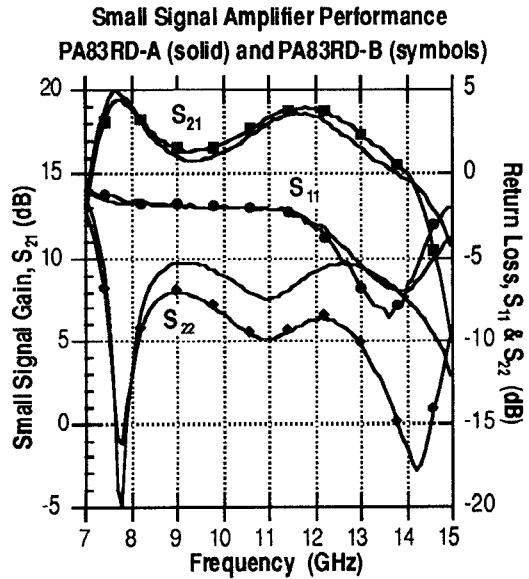

Figure 6. Measured small signal performance of circuits A and B at 7 V, 750 mA bias.

surements were used to extract small signal models. Pulsed IV data was used to extract large signal models. An internally developed modified Materka model was used for the large signal modeling.

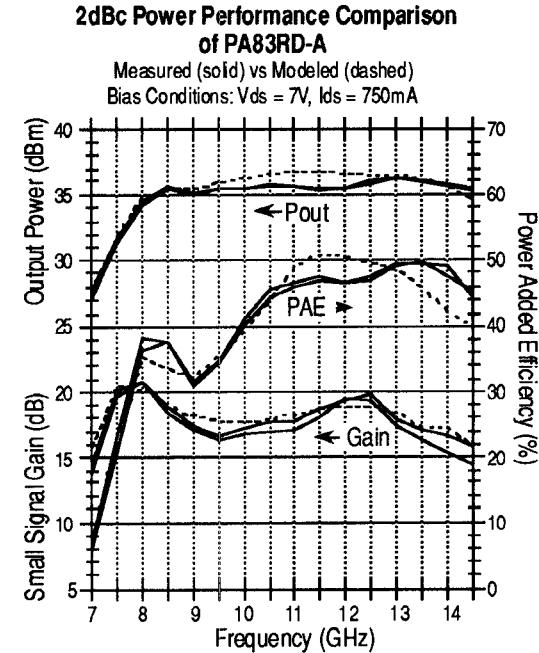

Figure 7. Measured vs. modeled large signal performance for circuit A.

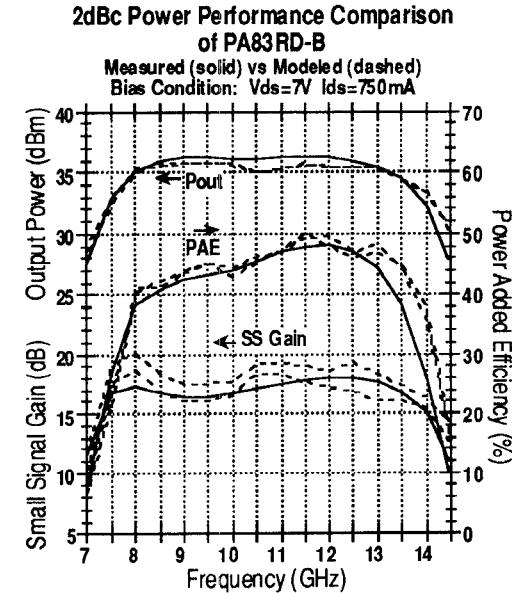

Figure 8. Measured vs. modeled large signal performance for circuit B.

## RESULTS AND DISCUSSION

Figure 5 shows measured results at 7 V drain bias for circuits A and B. Corresponding small signal performance is shown in figure 6. Both circuits achieve close to 50% peak PAE at 2 dB compression. Circuit A shows excellent performance at the high end of the band and circuit B shows excellent performance at the low end of the band. Both circuits provided 35-36 dBm output power over their operating band with small signal gain well in excess of 15 dB.

To analyze the efficiency performance further, load pull data was measured at 8 and 16 GHz on devices from the same wafers as the amplifiers. Analysis with the load pull data confirms that the efficiency performance can be attributed to the output match for both circuits. In circuit A, the output match moves away from its optimum value at the low end of the band. In circuit B, the output match moves away from its optimum value above 13.5 GHz.

Figures 7 and 8 compare measured and modeled output power and efficiency using the large signal model. The good agreement validates the large signal modeling.

## CONCLUSION

Two MMIC power amplifier results were presented using Raytheon's power PHEMT technology. Peak efficiency of 49.5 % was obtained at 2 dB compression and efficiencies in excess of 40% were obtained over much of the 8-14 GHz band. These results illustrate the effectiveness of the PHEMT as viable candidate for high efficiency power amplifiers in the X-Ku band.

## ACKNOWLEDGMENTS

The authors would like to thank L. Aucoin and A. Bertrand for wafer processing, W. Struble for device modeling, Z. Freitas and B. Engel for bonding, and G. Jerinic for management support and guidance.

This work was funded on MIMIC program under contract N00019-91-C-0210.

## REFERENCES

- [1] T. Apel, R. Bhatla, B. Lauterwasser, "High Performance Wide-Band & Medium-Band Power Amplifier MMICs", *1993 GaAs IC Symposium*, pp. 359-362.

- [2] F. Ali, A. Gupta, M. Salib, B. Veascl, D. Dawson, "A 2 Watt, 8-14 GHz HBT Power MMIC with 20 dB Gain and >40% Power Added Efficiency," *IEEE Trans. MTT*, Dec. 1994, pp. 2635-2641.

- [3] F. Ali, M. Salib, A. Gupta, D. Dawson, "A 8-15 GHz, 1 W HBT Power MMIC with 16 dB Gain and 48% Peak Power Added Efficiency," *1993 GaAs IC Symposium*, pp 363-366.

- [4] G. Ferrell, L. Dickens, J. Gipprich, B. Hayes, F. Sacks, "A High Efficiency 10 Watt HBT Power Amplifier Assembly using combining Techniques," *1995 IEEE MTT-S Digest*, pp. 327-330.

- [5] M. Mendes, S. Bouthillette, M. Cardullo, C. Page, S. LeSage, D. Danzillio, J. Cartland, "A High Efficiency PHEMT X/Ku Band Power Amplifier," *1994 GOMAC Conference Proceedings*.

- [6] J. Huang, G. Jackson, S. Shanfield, A. Platzker, P. Saledas, C. Weichert, "An AlGaAs/InGaAs Pseudomorphic High Electron Mobility Transistor With Improved Breakdown Voltage for X and Ku-Band Power Applications," *IEEE Trans. MTT*, May 1993, pp. 752-759.

- [7] A. Platzker, W. Struble, K. Hetzler, "Instabilities Diagnosis and the Role of K in Microwave Circuits," *IEEE MTT-S Digest*, pp. 1185-1188, 1993.

- [8] W. Struble, A. Platzker, "A Rigorous Yet Simple Method For Determining Stability of Linear N-Port Networks," *1993 GaAs IC Symposium*, pp. 251-254.